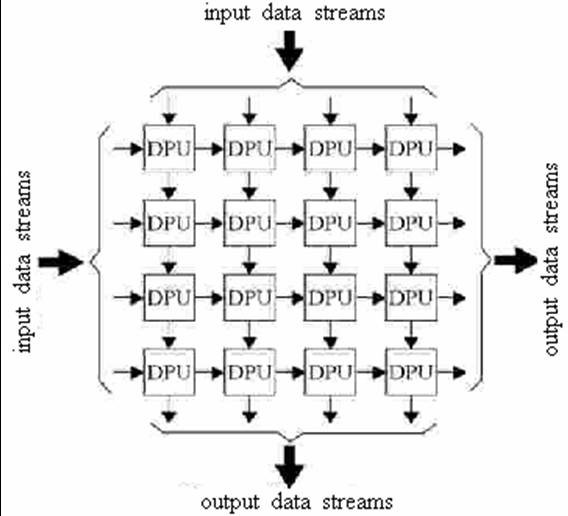

Systolic arrays are a latency-efficient way to compute matrix calculations - specifically matrix multiplication. Sparse matrices cause under utilization of the array because of the zeros. In an attempt to boost utilization, these empty cycles can be used to compute results of a different calculation thread thus also boosting overall performance. This project goal implementing a regular systolic array as well as a multi threaded systolic array in FPGA to...

Categories:

Algorithms implementation