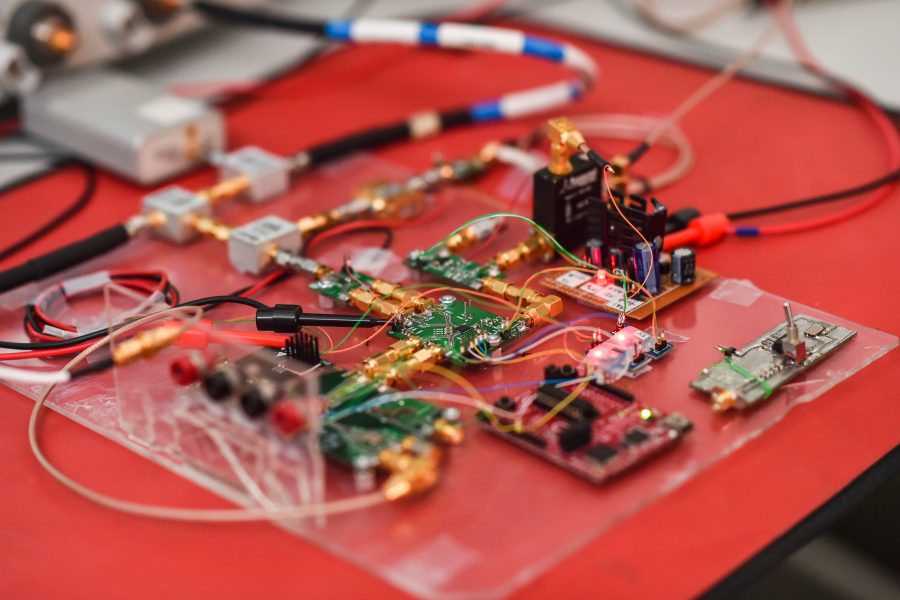

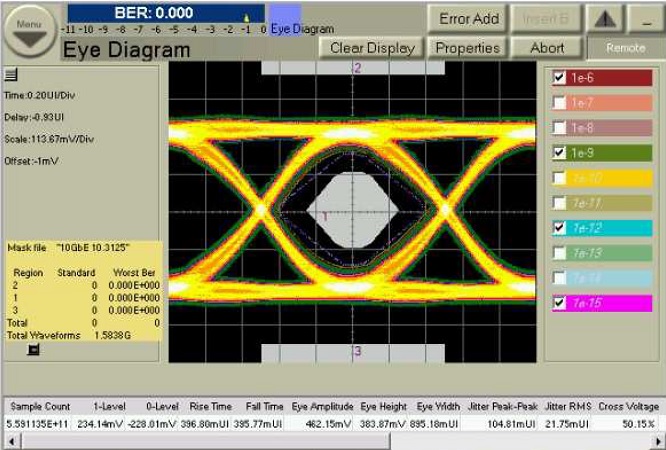

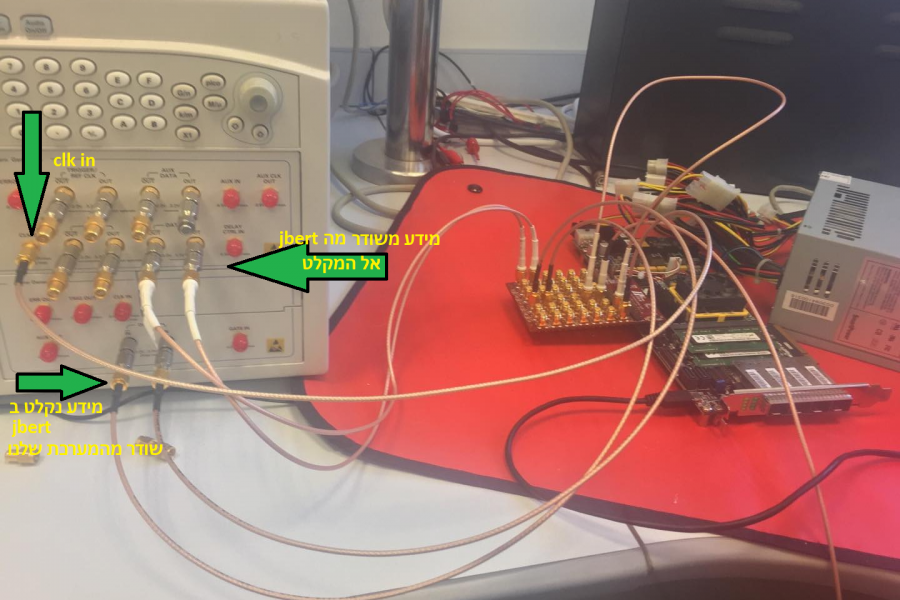

Fast communication channels have become a necessary infrastructure in any digital system. Industry defines various standards for transmitting data, one of the most important and common ones is the PCIe. The goal of the project is to design designing and building a serial data receiver using the FPGA board, which receives data from the Jbert and forward it to transmitter which transmits it back to the JBERT and analyze the...