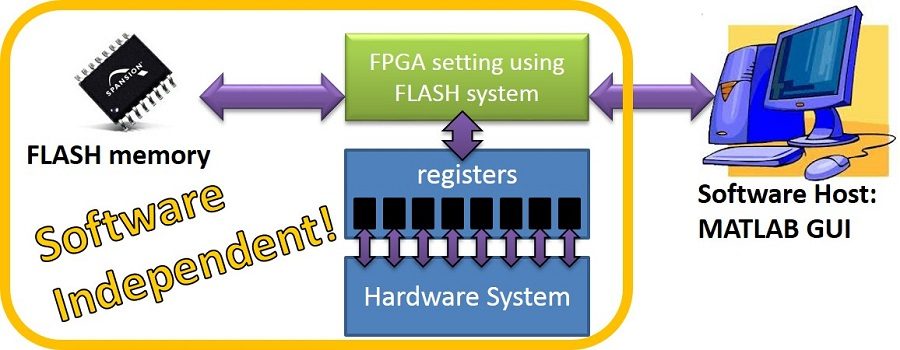

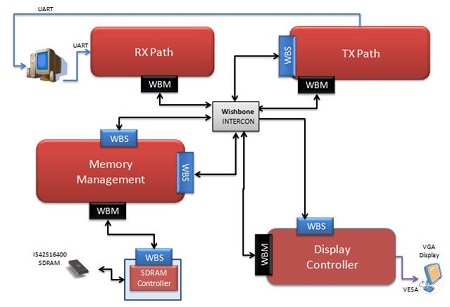

The Symbol Generator includes a software symbol generator (using Matlab) with a HW extractor (FPGA) using VHDL. Using a set of known symbols (such as letters, digits, icons, etc), all having in common the same dimensions, and are generated on the screen. The goal is to save time, resources and bandwidth. Therefore, the SW transfers to the HW only the change of the wanted frame from the current one, using...