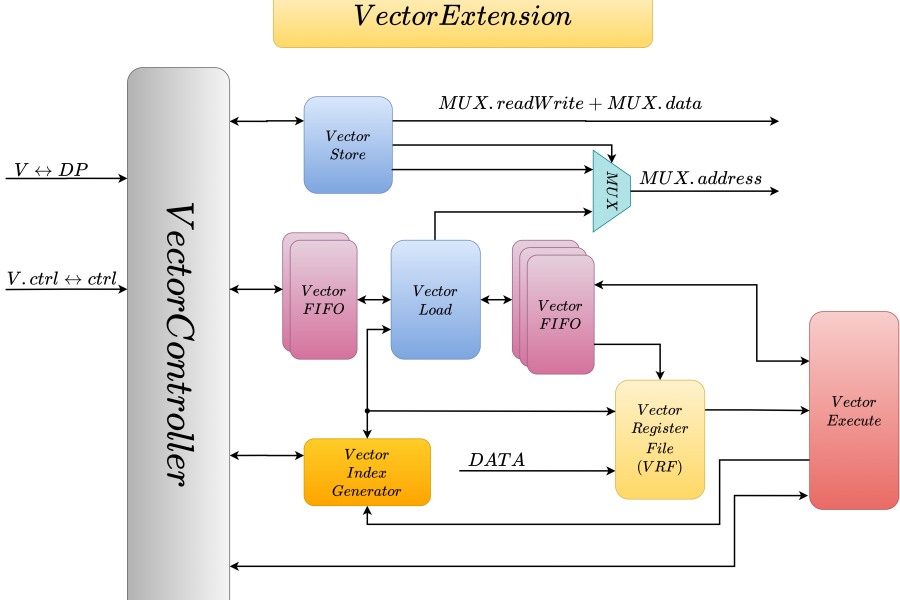

This project explores a simple design and implementation of a Vector Processing Unit attached to a RISC-V Multi-Cycle microarchitecture core. We implemented the design on an FPGA, executed code, measured and compared performance and power on the integer-processor versus our vector-processor. The comparative evaluation showed that in the cost of quadruple the hardware, we got significant differences in favor of vector-processor, both in energy and execution time.

Categories:

Algorithms implementation