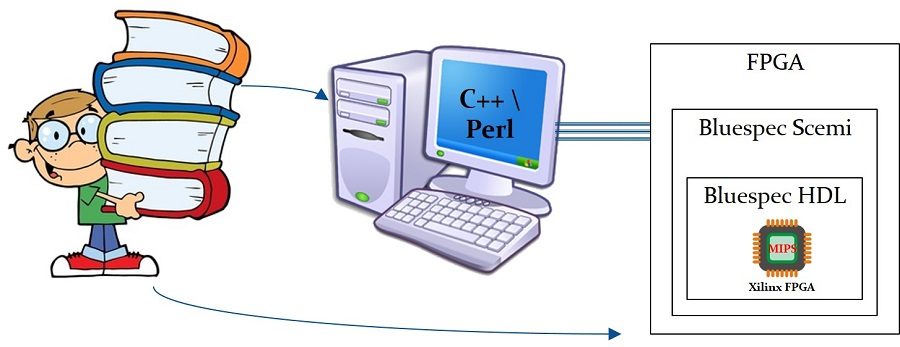

Bluespec SystemVerilog (BSV) is very high-level, fully synthesizable hardware description language (HDL). In this project we implement RISC multi core processor using Bluespec while relaying on 2 stages pipeline SMIPS single core processor. The multi core design shall be evaluated and analyzed compared to single core design in order to examine performance improvement.