The VGA Monitor Simulation project replaces physical VGA hardware with a software-based solution using VHDL, System Verilog, and C++ (SDL2). By generating and rendering VGA signals in simulation, it provides a flexible, low-cost platform for testing, education, and digital design prototyping.

Traditional VGA display systems rely on physical connectors and dedicated hardware, which limits portability and flexibility in testing and development. The goal of this project is to design a modular, software-driven VGA simulation system that overcomes these limitations by replacing the physical VGA interface with code.

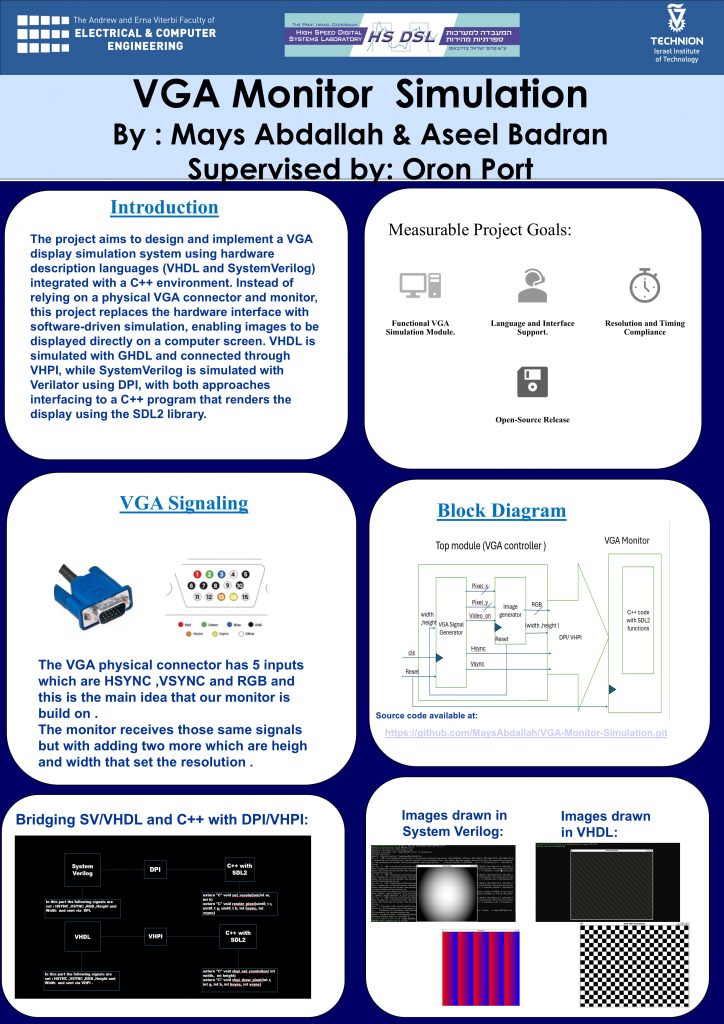

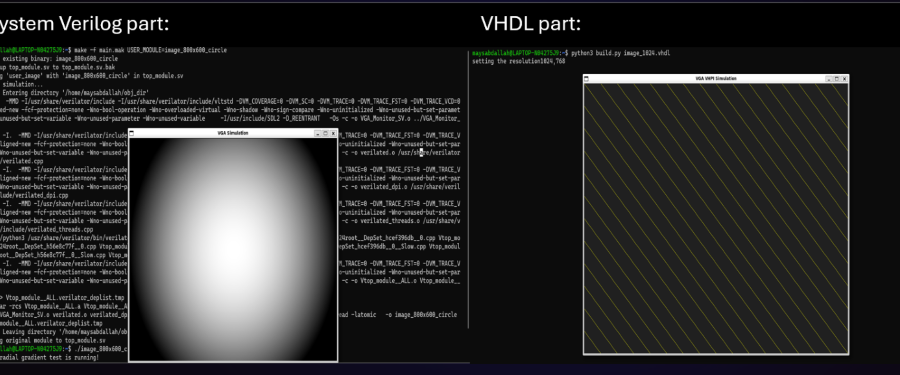

The project contains parallel flows: one using VHDL simulated with GHDL and VHPI, and another using SystemVerilog simulated with Verilator and DPI. Both flows connect to a C++ application that uses the SDL2 library to render the VGA output directly on the computer screen. The system generates standard VGA signals (HSYNC, VSYNC, pixel clock, and RGB values) and maps them to images provided by the user.

This design eliminates the need for external VGA hardware while maintaining accurate signal timing and resolution support. Tested resolutions include 640×480 ,800×600, 1024×768 and 1280×960 , with successful real-time rendering of static images such as circles, checkerboards, and gradients.

Final implementation demonstrates a practical, modular simulation framework that can be extended for animations, higher resolutions, and educational use in digital design and computer architecture.