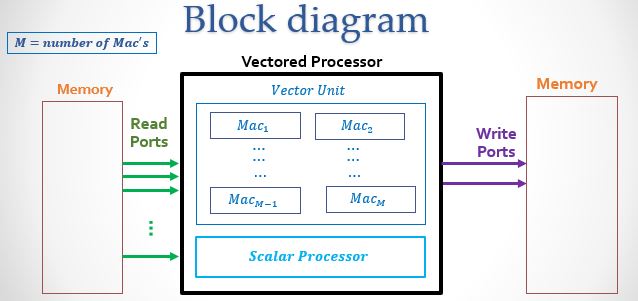

The goal of this project was first to design a vector accelerator for MIPS architecture that will perform dot product over two vectors of variable size, and to allow co-existing the two processors together. Later, the accelerator was tested and simulated for time, area and power consumption.

Dot product is a mathematical operator which is performed over 2 vectors, each of size N. Therefor the dot product includes performing N multiplications, between the first element of each vector and so on, N times. Afterwards one must add all these multiplications results which are another N-1 actions (in naïve approach). The total actions number is of order N.

This operator constitutes as the foundation of many algorithms used in signal & image processing and also deep learning & artificial neural networks. These numerous calculations are performed usually over very large vectors (N is a large), thus it’s highly needed to enable acceleration of the execution time while taking other parameters into consideration such as the area of the total system and the power consumed during the calculation.

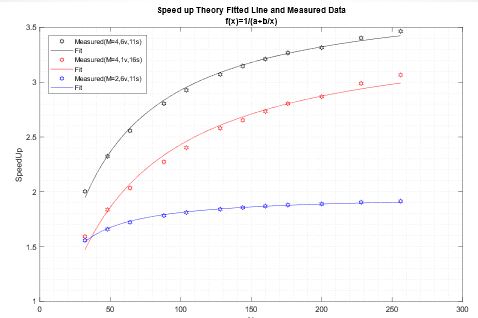

While it’s possible to design improvements and optimizations for the algorithms themselves, this project will focus on the architecture and micro architecture level of the processor which performs the calculations within the algorithm. Thus, the goal of that project is to find an efficient implementation in terms of execution time, area and power consumption followed by a micro-architecture level design of a processor capable of performing the vectored action, the dot product, along with varied scalar action, supported in basic MIPS architecture.

Therefor in this project the design principles will be presented along with an example of activation which will focus on time, area and power consumption.