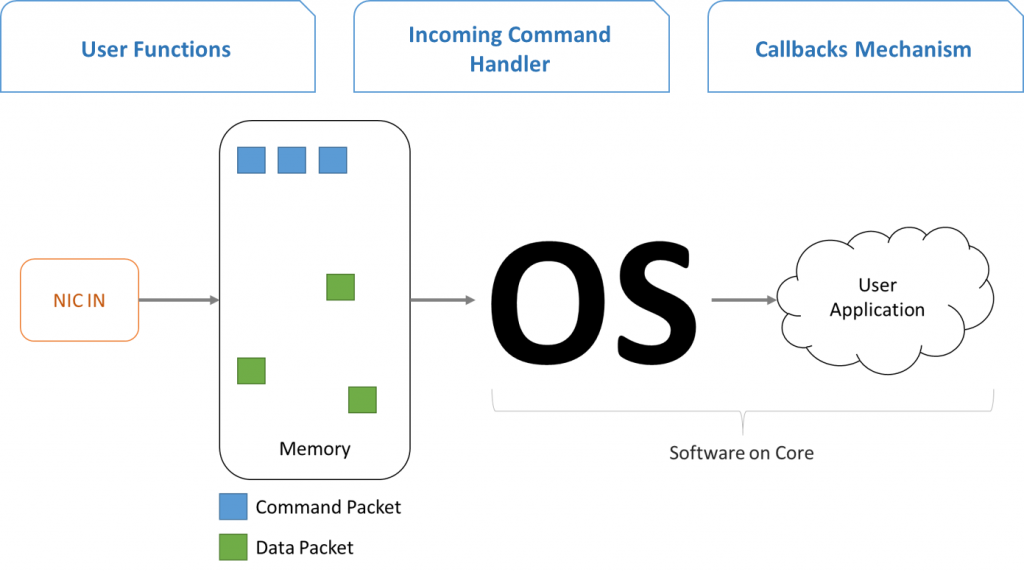

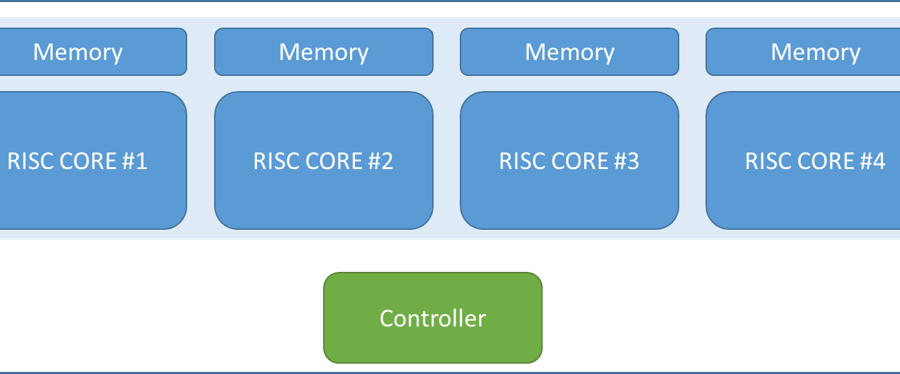

The project simulates a message-based, on-chip network architecture which inter-connects many ARM processors together using non-shared memory model. The project aim was to deliver scalable architecture for highly-parallel applications. The simulation was done in custom made software simulator on Linux operating system.

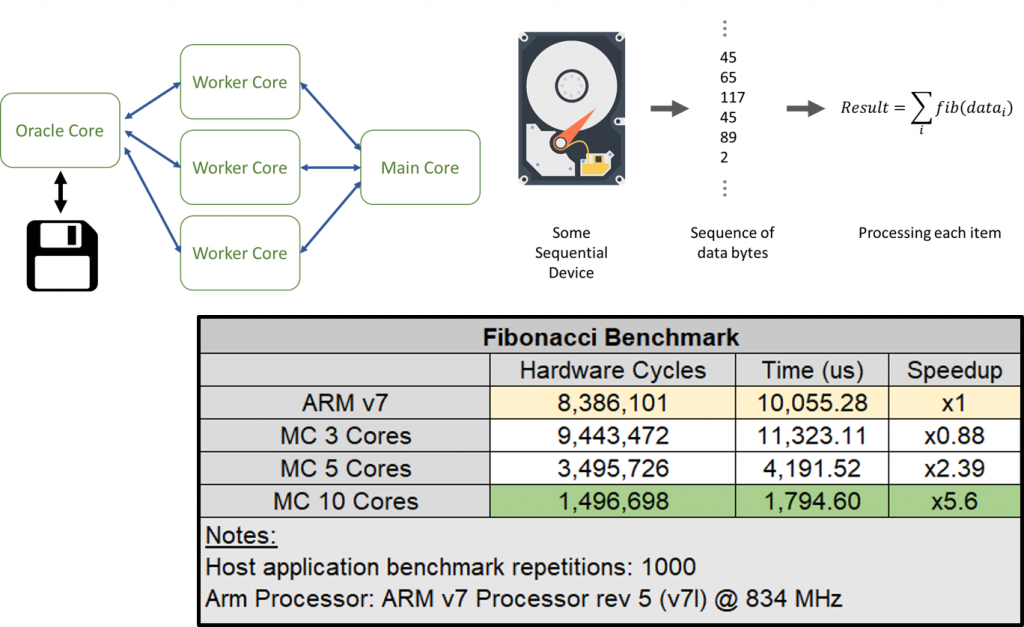

The project’s goal is to simulate message-based, on-chip network architecture for highly-parallel applications. The architecture aim to connect large number of CPUs together without changing its architecture. The memory model is such that each CPU has its own physical memory, thus no shared memory protocols are needed. Moreover, the suggested architecture is highly scalable and no major micro-architecture changes are needed when scaling. The project’s work covers the architecture, micro-architecture, communication protocol, light operating system and custom made simulator environment. The results were tested using two different benchmarks: one to simulate high network traffic, the other to simulate a combination of high network traffic with heavy computations. The results correspond with Amdahl’s law and present an increase of up to 5.6x in performance comparing to single ARM processor.