Implementation of an integer image convolution accelerator on an FPGA, with the attempt to minimize space usage and parallelize convolutions for multiple pixels at once, contributing to the overall speed of the processing of a frame.

Linear image filtering is a widely used mathematical operation on 2D datasets. It is used for many different applications and purposes, such as image processing and machine learning.

With the datasets becoming large, there is a growing need for acceleration of image convolution computation.

In recent years, with the rise in popularity and availability of FPGAs, many researchers have taken up the challenge to accelerate image convolution computation via FPGAs in a scalable manner.

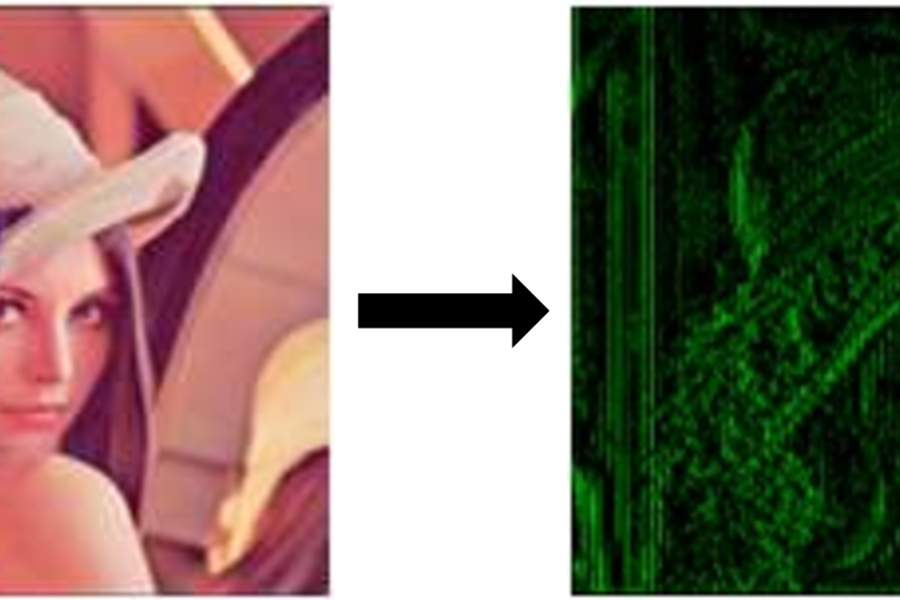

This project proposes one such implementation, focusing on simple integer image convolution, with the attempt to minimize space usage and parallelize convolutions for multiple pixels at once, contributing to the overall speed of the processing of a frame.

The accelerator is capable of performing convolutions for images with 12bit pixels and 640×480 or 320×240 in size, reaching ~65FPS and ~260FPS respectively.

The aim of the project is to build a fully functional integer-image-convolution module on the Xilinx Nexys 100T FPGA. The module will accept an image frame and a convolution kernel, will compute the convolution, and will return the result.

The proposed accelerator is compatible and integrated into the open-source VeeRWolf project, which comprises a RISC-V core synthesized on the Nexys 100T FPGA, a wishbone bus, and peripherals.

The accelerator sits as a wishbone slave, memory-mapped to a specific memory range, and can be controlled from software running on the RISC-V core.

A complementary RISC-V program, as well as a remote python client and a GUI wrapper, were also implemented as part of the project, to simplify interaction with the accelerator.