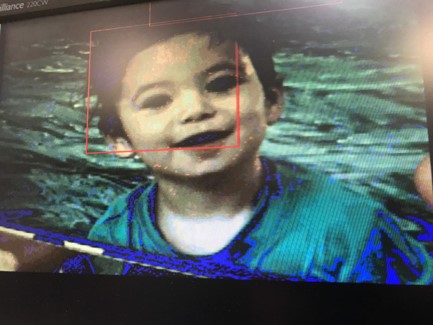

The ability to detect faces in live video is useful for many applications: cameras auto-focus, surveillance cameras, etc. The Viola-Jones algorithm was designed to deal with this problem using pre-trained filters to classify parts of the image as faces or none. To apply the algorithm on live video, our system is a HW implementation of the algorithm running on streaming video from camera and displaying live results on monitor.

The Viola-Jones algorithm passes each candidate rectangle in the processed image through a Haar wavelet filter and then runs the outcome through a cascade of pre-trained filters (around 3k of them). Only a rectangle which passes all the cascade of filters is considered a positive face detection.

Due to the independency of image rectangles of each other, the algorithm efficiency can be significantly improved with dedicated parallel hardware. Rather than integrating the frame and running the entire cascade of filters on every rectangle in the image serially, an array of such filters can process separate rectangles concurrently and complete entire frame processing in a higher rate.

Our project is an implementation of such hardware solution on Xilinx’s ZedBoard – based on a reference project implemented on an Altera device.

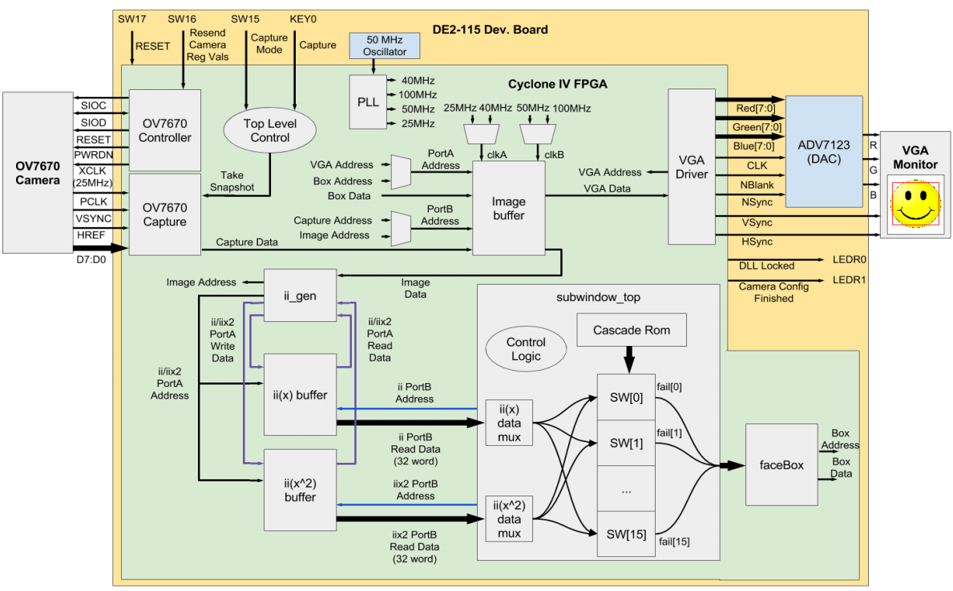

The design consists of video modules (camera capture and VGA monitoring), image integration machine, sub-window array of filters, detection boxes drawing machine, and a main FSM orchestrating the entire frame processing.