Analysis of power traces that were produced by inputting scan chains to the chip and trying to find correlation between the power trace that was outputted and the scan chain that was inserted.

In this project an algorithm and setup was were used to find a correlation between the scan chain and the power trace.

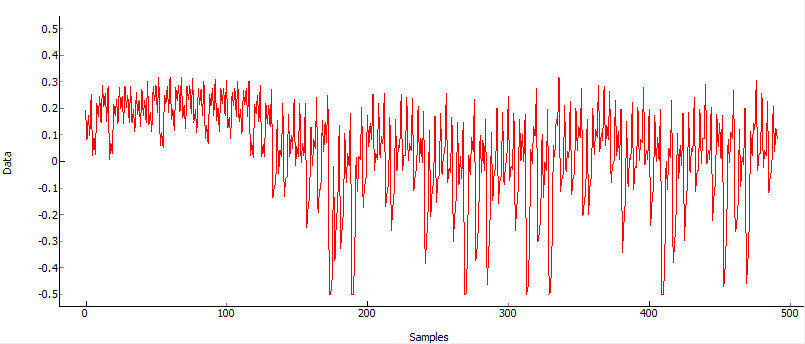

The main idea was to see if there was a way to retrieve information regarding the scan chain by observing the power trace that is created by the chips power consumption. In order to do this a side channel attack called a Template attack was used. The implementation of this attack was done by capturing thousands of power traces of the chips power consumption and then, finding the points of interest in the power trace. This was done using pairwise differences and other tools to find the points with the highest variance between them and their neighbors.

The results show a great impact of different parameters on the ability of the algorithm to predict the scan chain that was inputted. We show the feasibility of telling what scan chain was inserted based on the power consumption of the chip. Much more work in the area must be done.