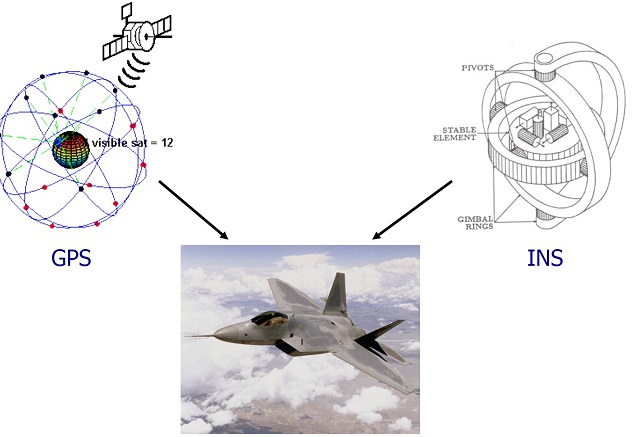

The subject of this project is to design and implement a combined software/hardware environment in which multiple algorithm computation units can be linked together across multiple FPGAs according to a certain multi-stage data flow. The multi-stage algorithm computation flow demonstrated by this project is the "Regularized Particle Filter using GPS/INS" algorithm . Particle filters are sequential Monte Carlo methods used to estimate various unknowns of a time-varying signal presented in real time. The RPF algorithm combines GPS/INS inputs intended for navigation systems.

System description

The system consist of four FPGAs containing computation units linked together by streaming units intended to ease flow controllers development.

The streaming units allow serialization/de-serialization of structured data words, handle DDR RAM/FIFO memory connections and also inter/intra-chip connections.

System’s inputs are INS and GPS readings received at the input FIFOs.

The INS reading is received every 10msec while the GPS reading is received once a second. Real-time requirements demand that both readings be handled within 10msec since arrival.

Each computation iteration involves the transfer of 30,000 data structures called particles containing 18 state variables, 24 bits each.