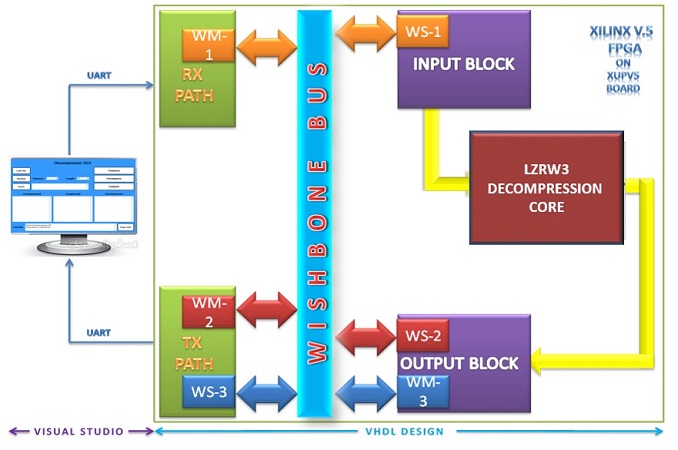

The project goal is designing high speed decompression core and assemble its periphery units using VHDL language so it could be properly implemented on an FPGA.

The implementation is comprised of the following parts:

GUI – The data flow process starts and ends at the GUI, using the GUI to transfer and receive data from the board the decompression core is implemented on. The GUI is also used to compare the results to the Golden Model output for the same input file. The GUI is implemented using visual studio development environment and provides a comfortable usage, testing and system analyze utility.

Rx PATH – the first unit on the FPGA that receives the input data from the computer. The data is sent by the GUI using the serial UART protocol. The unit discovers errors in the input data and parallels the data from 8 serial bits to a single byte before transferring it to the Input Block.

Input block – since the UART transfer protocol is very slow, in order to transfer the data to the core in high speed, the data has to be stored first on a memory, which will contain the whole compressed input data. After all compressed data has been stored, data will be transmitted to the LZRW3 decompression core in a rate of one byte per clock cycle (125 Mhz).

LZRW3 decompression core – receives the data in compressed LZRW3 format, processes it and provides decompressed data. The core works in frequency of 125 Mhz in both sides (Input/output ports).

Decompressed file memory (OUTPUT BLOCK) – contains a RAM memory that will hold the decompressed file and transfer it to the Tx PATH

Tx PATH – the path in which the output data will be transferred back to the computer (GUI) using the UART protocol as serial data.