The project implemented Internal Logic Analyzer, a checking device which assist debugging the FPGA card. The device is independent in the manufacturer of the card. The project was written in VHDL code. Both entering data into the system and extracting it are according to UART protocol. In the system there is a possibility for the user to define the depth and the width of the recorded data as he wishes, also he can define trigger type(out of four defined options) and determine the trigger position.

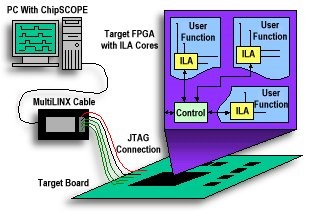

FPGA’s manufacturers supply debugging tool for labs, named Logic Analyzer. It allows recording of internal data in the FPGA and displaying it to the user.

The hardware part enters the FPGA’s code and includes memories to store the recorded data, logic aimed to configuration changes (e.g. trigger type), also logic that identifies trigger lock, and logic for sending the recorded data to the software.

The tool of the FPGA manufactures, Altera, is named SignalTap. The Xilinx tool is named

The project goal is to design an Internal Logic Analyzer for the FPGA, which will be independent in the FPGA manufacturer.

The hardware part includes building a system in VHDL, that allows recording of the chosen signals according to configuration and sending the recorded data back to the user.