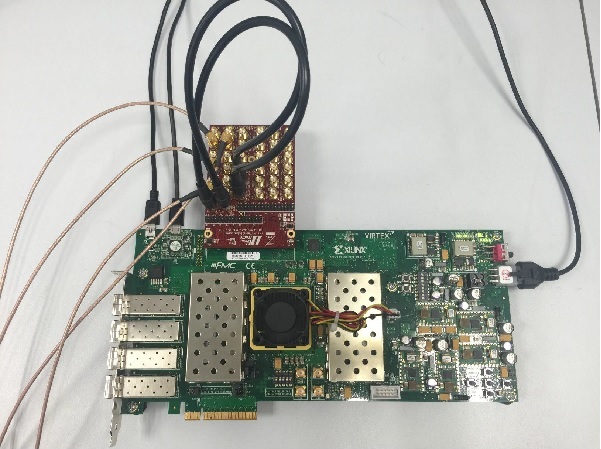

System for sub-nyquist sampling in SMPL lab at the EE faculty at Technion. It will provide a flow of pre-defined signals in high frequency (6.1 GHz) to the client system which would use the data in order to reconstruct sampled signals in sub-Nyquist rate.

The FPGA based system, takes data via UART interface, and according to pre-defined rules, sets it into 6 internal built-in memory blocks. From the memory blocks, the data is passed to 6 built-in SerDes (GTH’s), and from there is output to the client system.