Design and implement of the Heterogeneous Network-on-Chip (NoC) router system.

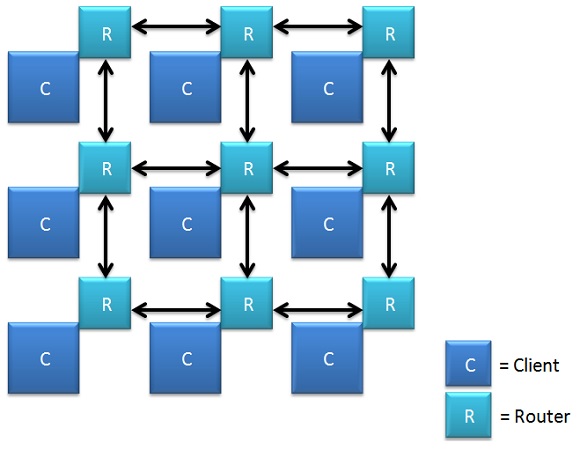

Network-on-Chip (NoC) is a new approach to design the communication subsystem of System- on-a-Chip (SoC) and Chip-Multi-Processors (CMP). In order to overcome the BUS bottleneck in bus based communications in SoC, a new communication paradigm, network on chip (NoC) has been developed. In the NoC paradigm, the SoC modules communicate though a network of routers. Each router is connected to all its neighbors and to one of the SoC modules. The router IO port protocol is chosen according to the requirements of the application. NoC brings networking theories and systematic networking methods to on-chip communication and brings notable improvements over conventional bus systems. In this project, a Shared Buffer architecture was chosen, designed and implemented in the Heterogeneous NoC router system. The use of a Shared Buffer as a main buffering unit between the input ports and the output ports of each router allows to reduce the total number of buffers in the router and maximize the measurement: performance per power.