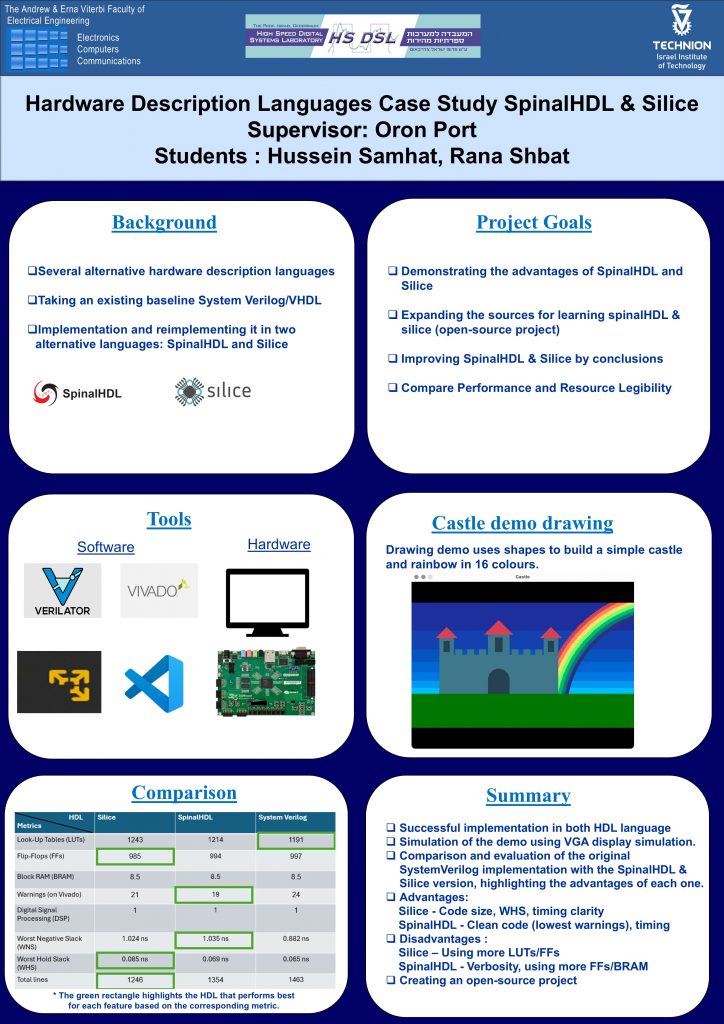

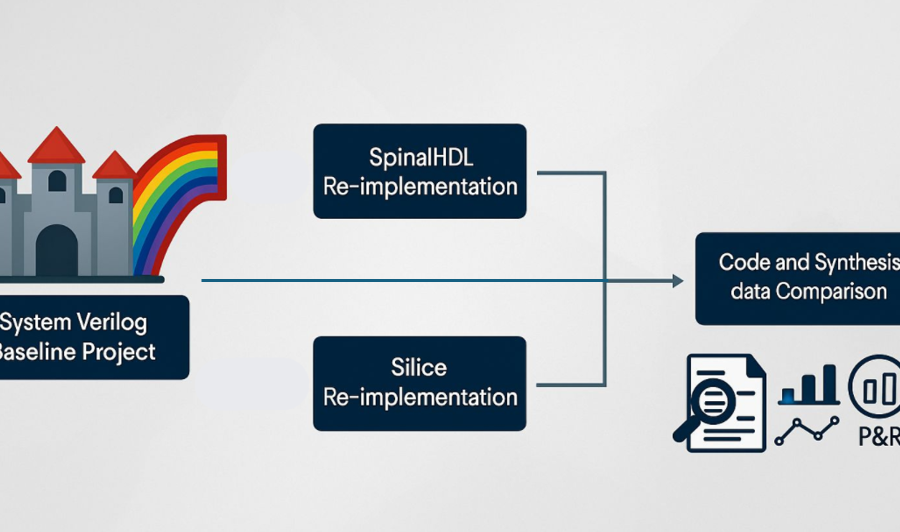

This project converts a SystemVerilog implementation of Castle Drawing to Silice and SpinalHDL, which are high level hardware description languages. It showcases the capabilities of Silice and SpinalHDL, compares it with SystemVerilog in terms of readability, and performance and provides feedback for language improvement.

This project focuses on translating an existing SystemVerilog implementation of a “Castle Drawing” graphics into SpinalHDL and Silice—two modern hardware description languages designed to improve design productivity and clarity. The original SystemVerilog code inculdes a collection of modules that render simple shapes (such as lines, rectangles, circles, and triangles) to generate a castle drawing.

The main objective of this project is to evaluate and demonstrate the strengths and limitations of SpinalHDL and Silice by comparing them to traditional RTL development in SystemVerilog. SpinalHDL, a Scala-based hardware language, leverages object-oriented and functional programming concepts to streamline hardware development. Silice, on the other hand, offers a C-like syntax and focuses on automating state machines and pipeline construction for better design abstraction.

The translation process involved preserving the algorithmic behavior and timing characteristics of the original design while adapting it to the syntax and structural paradigms of SpinalHDL and Silice. Special attention was given to the handling of FSMs and parameterized modules. Through this work, the project reveals key insights into how higher-level HDL abstractions can reduce boilerplate code and improve module reuse without sacrificing performance or clarity.

In addition, this project serves as a practical case study for engineers and researchers interested in adopting modern HDL methodologies. It highlights the expressiveness and maintainability offered by SpinalHDL and Silice and contributes to the growing body of translated, open-source hardware examples that bridge traditional and modern HDL development.