Alternative hardware description languages are studied by taking an existing baseline SystemVerilog/VHDL implementation and re-implementing it using two alternative languages: PipelineC and Amaranth.

In recent years, several alternative hardware description languages (HDLs) have been developed to simplify hardware development compared to traditional System Verilog and VHDL workflows. This project studies some of these languages by reimplementing an existing baseline System Verilog/VHDL design in two alternative languages.

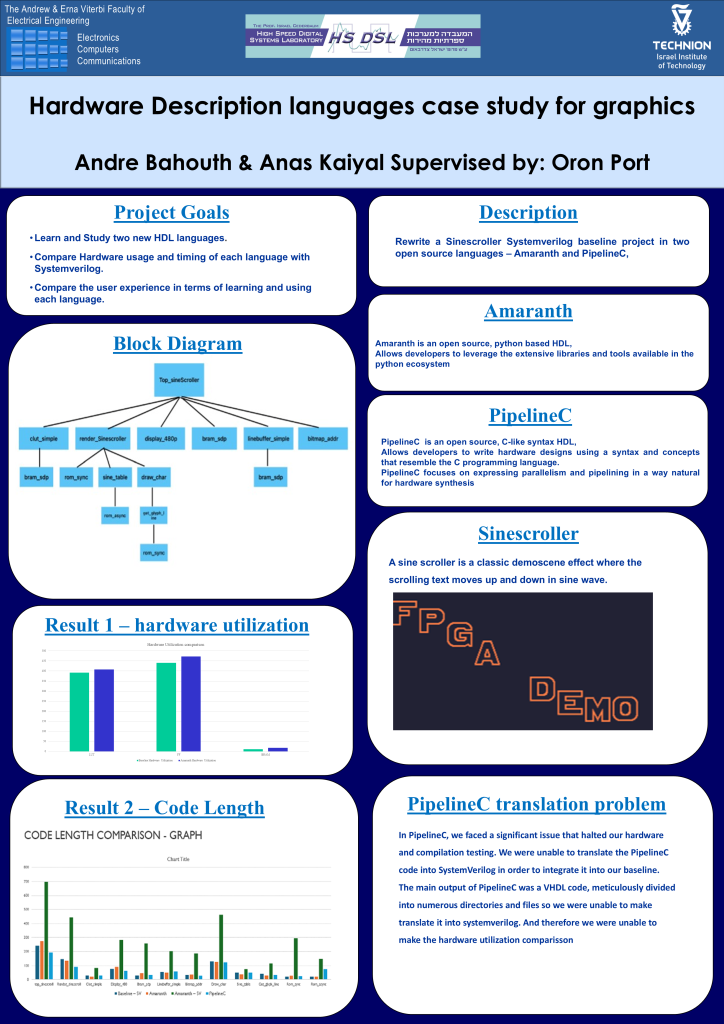

The study focuses on testing and analyzing Amaranth and PipelineC—two distinct HDL languages. Testing emphasizes two key aspects: first, the analysis of hardware usage and timing for each language, considering metrics such as the number of flip-flops, BRAMs, lookup tables, and other relevant resources. Second, the user experience is assessed, including the difficulty of learning and using each language, to identify which language performs best in various areas.

The baseline design is drawn from Project F—a compilation of projects implemented in System Verilog. Specifically, this study centers on the “sinescroller” project within Project F, using it as the baseline. The sinescroller will be implemented separately in both PipelineC and Amaranth for comparison.

A sine scroller is a classic demoscene effect where scrolling text moves up and down in a sine wave.