DMA is very wildly used method for the transfer of Data.

This project aims to develop an implementation of this method using System Verilog language.

In computer-based data acquisition applications, data incoming or outgoing through computer I/O devices must often be managed at high speeds or in large quantities.

The three primary data transfer mechanisms for computer-based data acquisition are polling, interrupts (also known as programmed I/O), and direct memory access (DMA).

The project focuses on implementing the DMA method which has several advantages over the other two methods making it faster due to it allowing access to the memory without the need of the CPU’s interference.

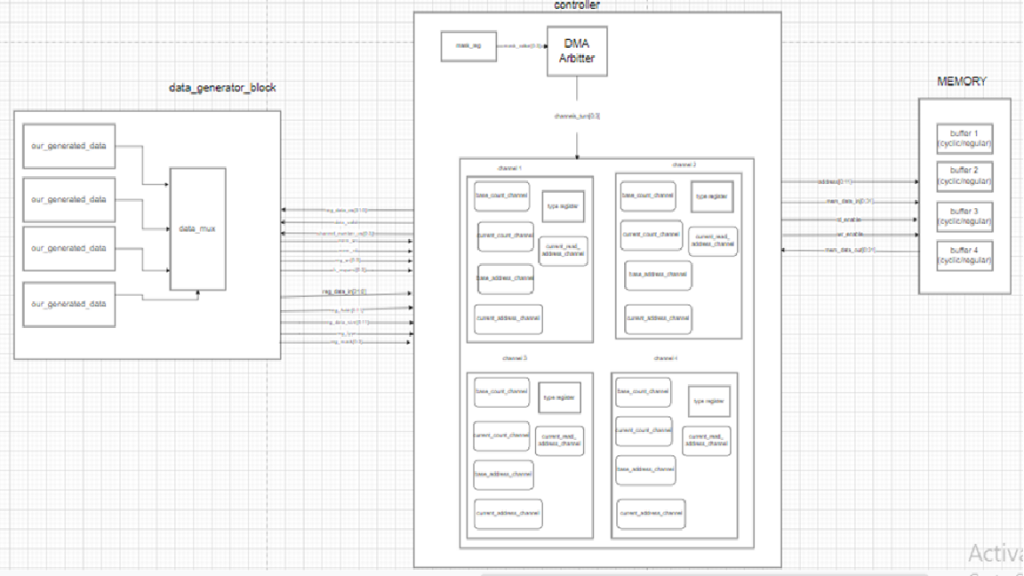

In addition, project implements a DMA controller which is made up of: 4 DMA channels and a DMA arbiter among other elements, as well as the Data Generator which is controlled by the user and allows us to send the needed read and write operations to the DMA controller and also checks if these operations were executed correctly right after.

When the system is first activated 4 memory buffers are allocated in the “memory” (our version of it). These buffers can either be: cyclic or regular and each one of the four channels saves the parameters that are relevant to one of the four buffers. Right after that we start performing read and write instructions in a round robin method while taking into consideration that each channel is responsible for one buffer and that if a channel is masked then it is skipped.