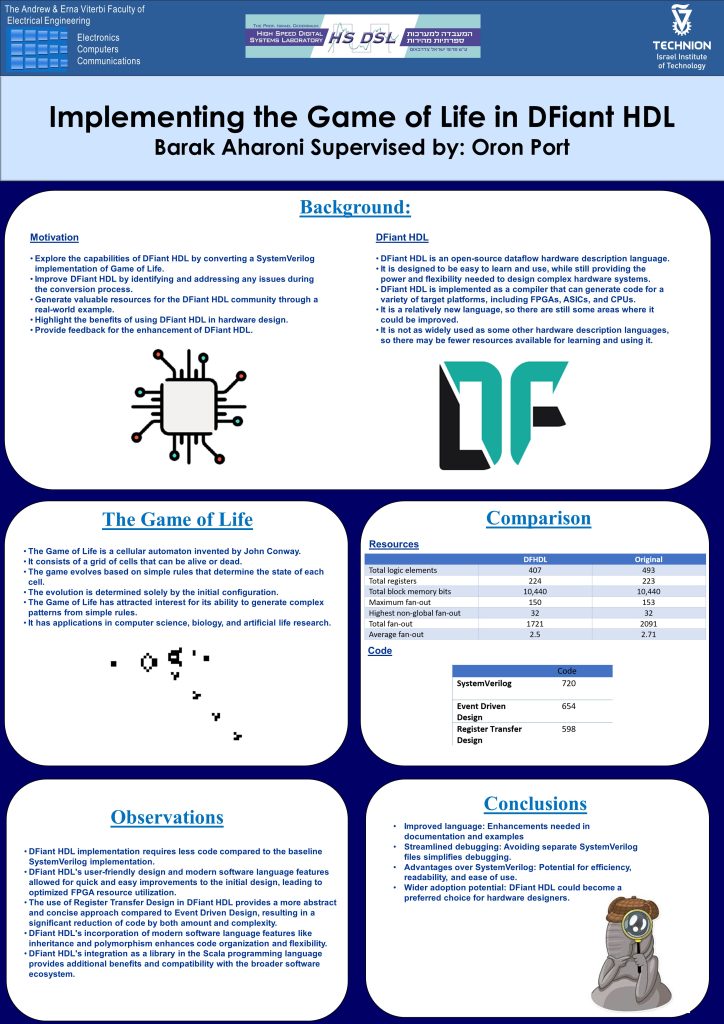

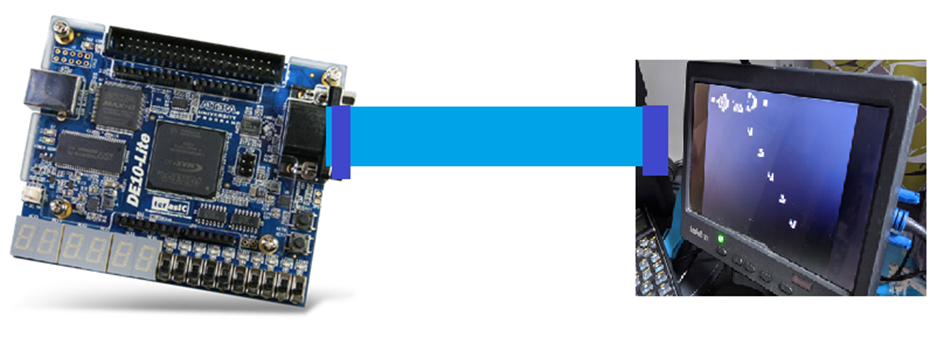

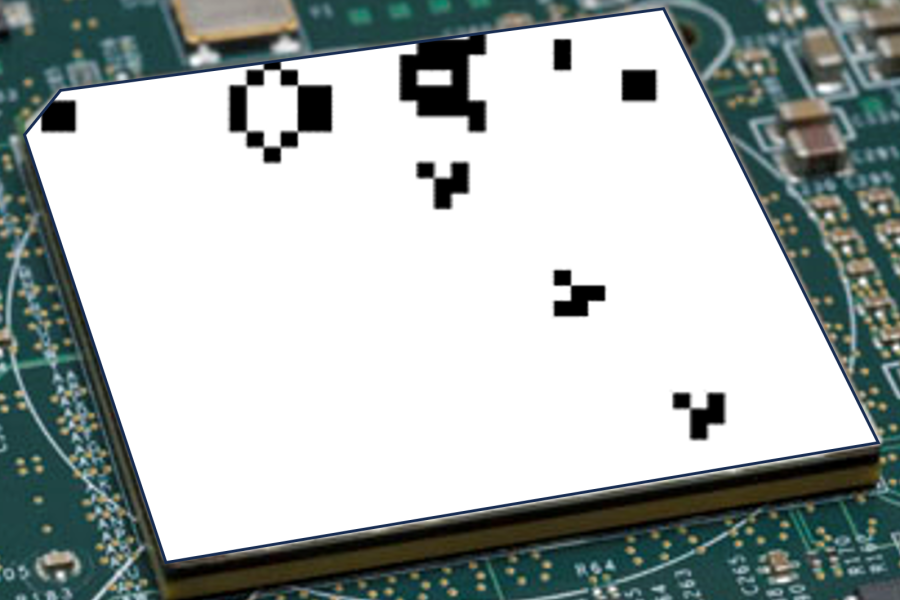

This project converts a SystemVerilog implementation of the Game of Life to DFiant HDL, a hardware description language. It showcases the capabilities of DFiant HDL, compares it with SystemVerilog in terms of readability, and performance and provides feedback for language improvement.

This project aims to convert an existing SystemVerilog implementation of the Game of Life cellular automaton to DFiant HDL, a dataflow hardware description language (HDL) embedded as a library in the Scala programming language. DFiant HDL offers a unique approach to hardware description by providing a timing-agnostic and device-agnostic solution. It combines dataflow firing rules, modern software language features like inheritance and polymorphism, and traditional HDL elements such as bit-accuracy and input/output ports.

The primary objectives of this project are to showcase the capabilities of DFiant HDL by comparing the readability and performance of the original SystemVerilog implementation with the DFiant HDL version. By identifying and addressing any challenges encountered during the conversion process, the project aims to contribute to the ongoing development and improvement of DFiant HDL.

Furthermore, this project endeavors to generate valuable resources for the DFiant HDL community by presenting a real-world example of how the language can be effectively employed in the design of digital systems. Additionally, it explores how the modern software language features incorporated in DFiant HDL can enable a more advanced and streamlined design process.

This project successfully converts a SystemVerilog implementation of the Game of Life to DFiant HDL, showcasing the language’s capabilities in terms of improved readability and performance. Valuable insights have been gained to enhance DFiant HDL, benefiting the hardware design community. The project also highlights the potential of DFiant HDL’s modern software language features for advanced and streamlined design processes. Overall, it demonstrates the advantages of using DFiant HDL in hardware design and contributes to its continuous improvement.