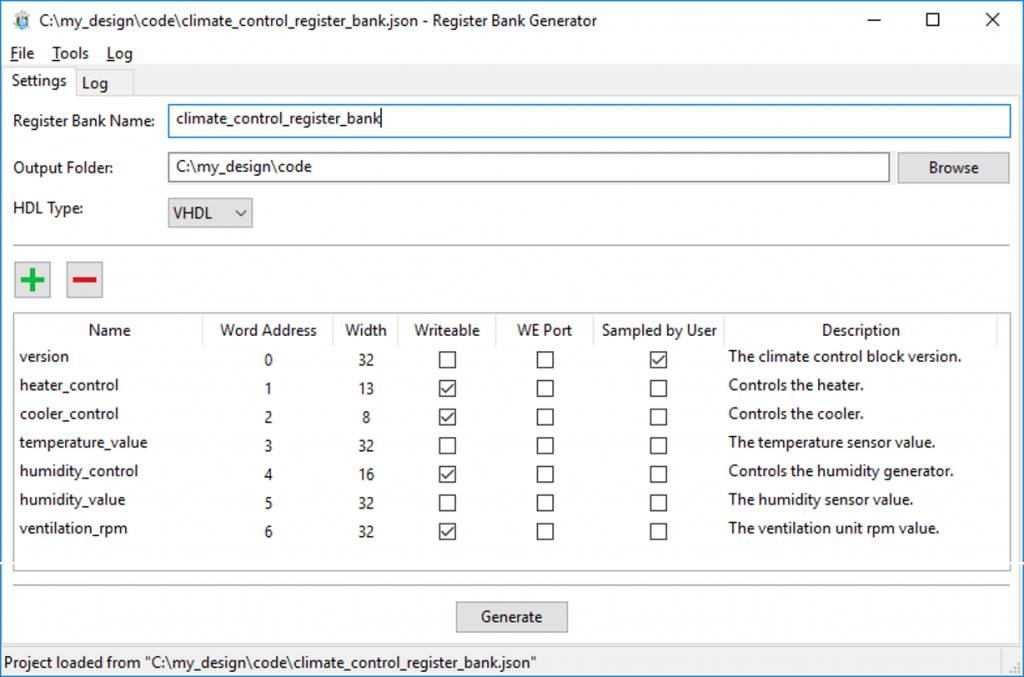

This project creates a tool for generating project specific register banks.

Register banks are a major part of SW-HW interfaces, which are common in SoPCs, and their implementation can be generated by automated tools.

The tool supports:

Generation of register bank HW blocks (VHDL/Verilog), which connect to vAXI.

Generation of SW header files (.h files), for accessing the HW registers.

Generation of utilization reports.

User configuration of each register:

Name.

Address, including support for unaligned and/or non-continuous addresses.

Width.

Access (Read-Only / Read-Write).

Additionally, the project contains an example design for using the generator tool – matrix-vector multiplication:

The multiplication is performed on a HW accelerator block.

The SW that handles data transfers to and from the accelerator.