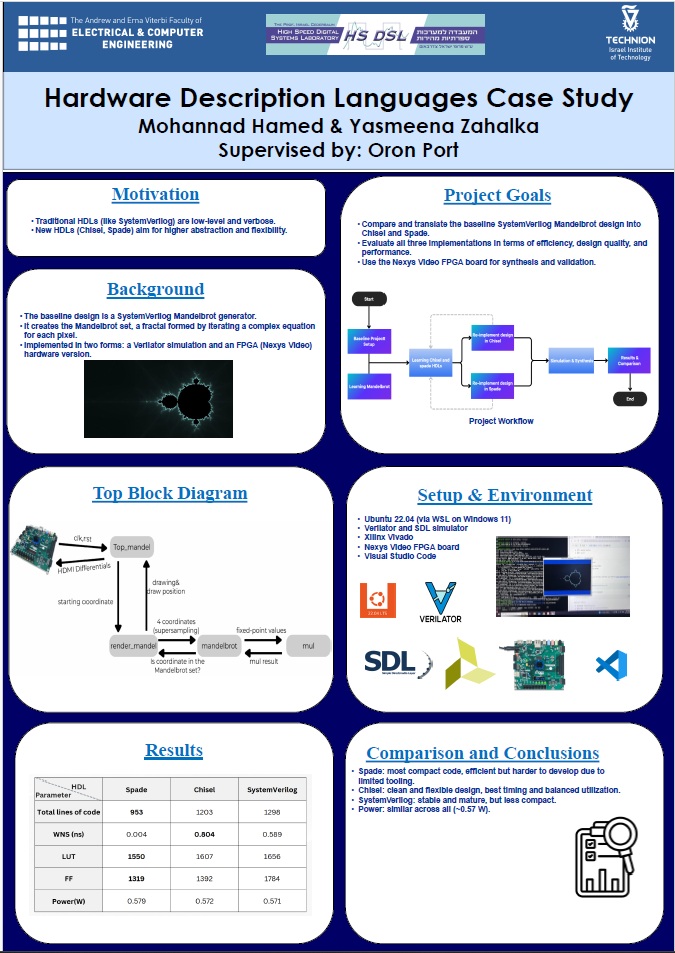

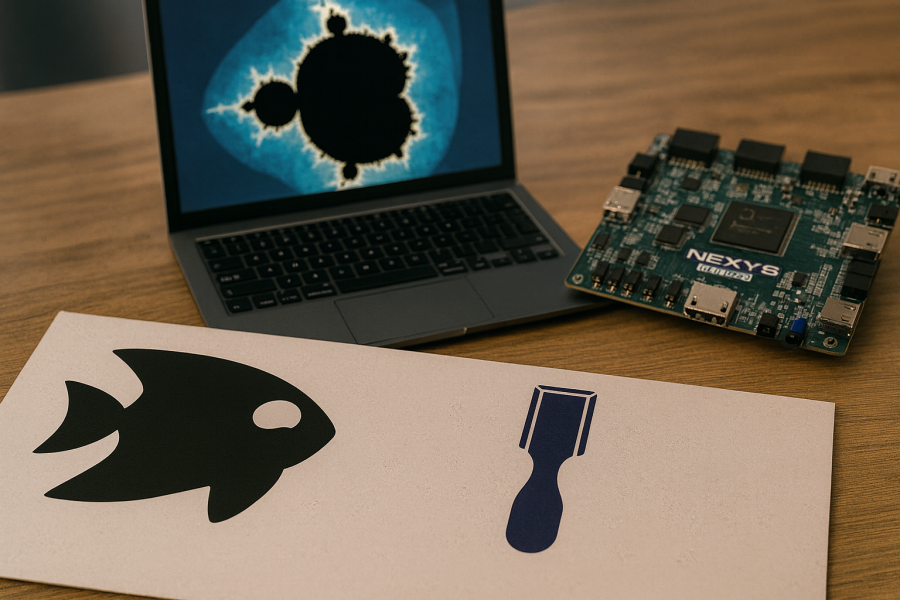

This project re-implements a baseline SystemVerilog Mandelbrot renderer in Chisel and Spade, targeting the Digilent Nexys Video FPGA, and compares the approaches on resource usage, timing, and code size. The work includes an SDL/Verilator preview path and a full DVI/TMDS pipeline on hardware.

The project explores modern hardware-description paradigms by porting a reference SystemVerilog Mandelbrot design to Chisel and Spade, then evaluating the resulting implementations on an Artix-7 Nexys Video board. The baseline renders the Mandelbrot set using fixed-point arithmetic and a small framebuffer; the team reproduced the full pipeline, including debouncing, line-buffering with BRAM, a render core, and a DVI/TMDS video path, while also providing a software preview flow via Verilator + SDL. Methodologically, the work emphasizes clean clock-domain handling (system/pixel), MMCM-based clocking, and deterministic pipeline staging so that each HDL’s generated RTL remains comparable. The evaluation focuses on three axes: (1) resource utilization (LUTs/FFs/BRAM) to understand synthesis quality; (2) timing closure via worst negative slack (WNS) under identical constraints; and (3) code density/maintainability, contrasting low-level RTL with higher-level generators. The outcome demonstrates that Chisel and Spade can faithfully reproduce the behavior of the SystemVerilog baseline while enabling more expressive source code and rapid iteration, especially when integrating with modern tooling and open-source simulation. The project materials include environment setup, flow diagrams, and side-by-side examples to highlight how each HDL expresses the same hardware intent, offering a practical comparison of productivity and performance trade-offs across languages.