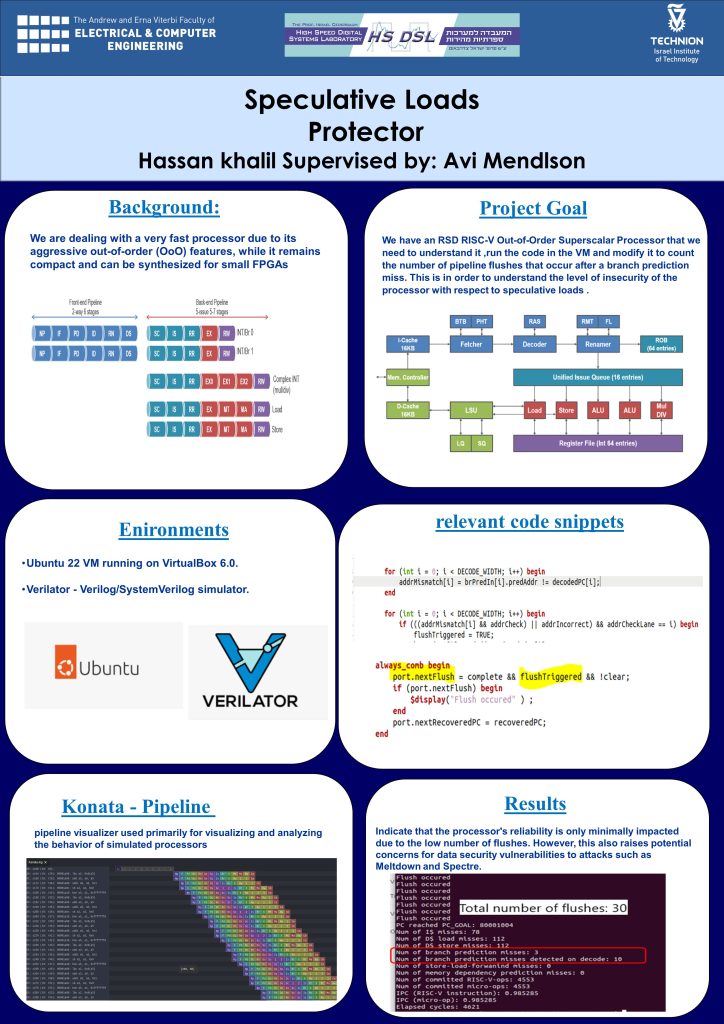

A very fast processor is being dealt with, characterized by its aggressive out-of-order (OoO) features, while it remains compact and capable of being synthesized for small FPGAs. The models responsible for identifying branch prediction misses and flushing the pipeline are to be distinguished, and counted upon running a certain test.

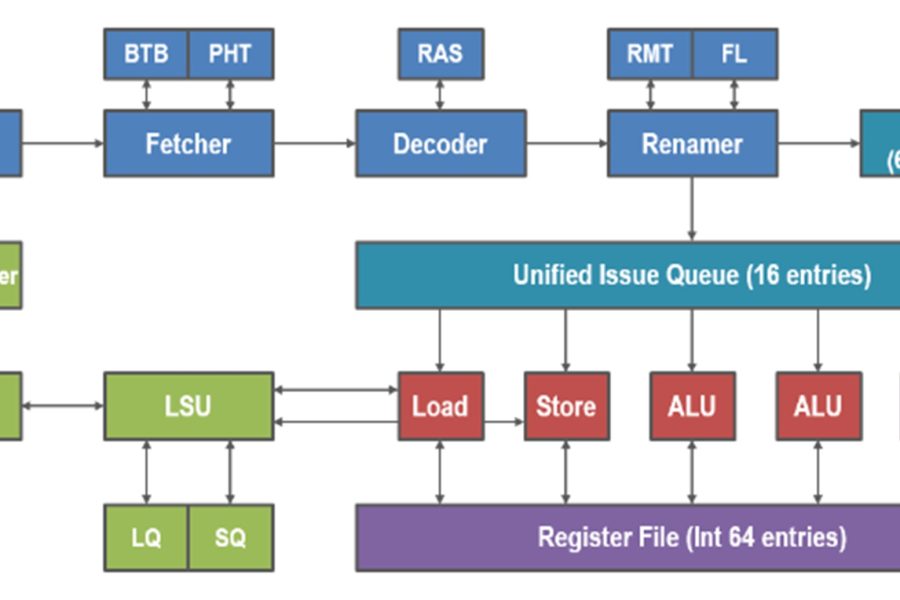

The RSD RISC-V Out-of-Order Superscalar Processor is under examination, with the objective to understand, run the code, and modify it to count the number of pipeline flushes occurring after a branch prediction miss. This effort aims to gauge the processor’s level of insecurity concerning speculative loads.

The attention is centered on the modules responsible for branching decisions and pipeline cleaning in cases of misprediction: At this stage, a deep dive into the SystemVerilog-written modules is undertaken. Upon grasping the code, focus shifts to two pivotal modules:

- The sv, situated within the decode stage files, embodies logic designated for identifying branch mispredictions and dispatching a flush trigger signal to the pipeline, thereby initiating a necessary flush.

- The sv, a component of the pipeline files, samples the flush trigger value (true or false). It ensures the command is complete and not merely an empty instruction, subsequently triggering a pipeline flush to expunge the instructions.

It is observed in the final analysis that 30 flushes transpired following 13 branch prediction misses during the test, spanning nearly 4600 cycles. This translates to a minuscule percentage of cycles resulting in the pipeline being flushed, indicating only a minimal impact on the processor’s reliability. Nonetheless, it surfaces potential concerns regarding data security vulnerabilities to attacks like Meltdown and Spectre.