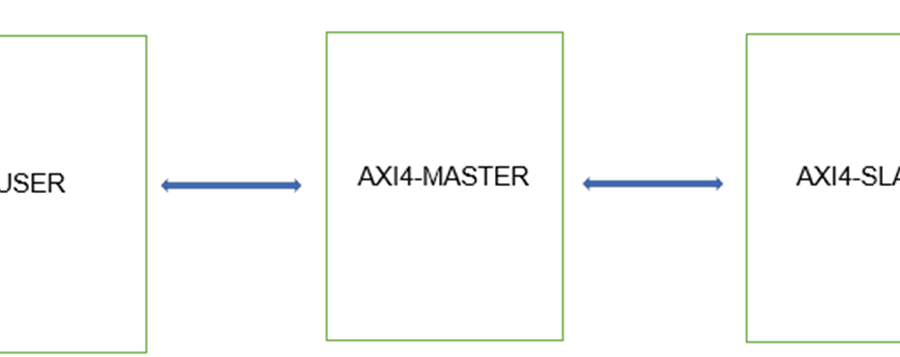

Implementation of axi4 master according to axi4 protocol

and integration with axi4 slave(from Xilinx) into Zedboard to verify them.

The axi4 master will support separate address/control and data phases,

support for unaligned data transfers, using byte strobes,

uses burst-based transactions with only the start address issued,

separate read and write data channels that can provide low-cost Direct Memory Access (DMA),

support for issuing multiple outstanding addresses,

in a nutshell is to build a smart interface for memory

the implementation is done by using hardware description language in our case is system Verilog,

then verify the master by connect it to axi4 slave that we get from our mentor and import them into the zedboard.

To verify the master, we use a checker that we get from the mentor, connected to the master slave interface,

this component has the ability to detect error in the signal level that don’t go according to the protocol,

we use other component from the library of Vivado like native fifo that we used in the master model.