Design an I2C Master controller capable to initiate write and read operations. Implementation of I2C Master as an IP block using Xillinx Vivado.

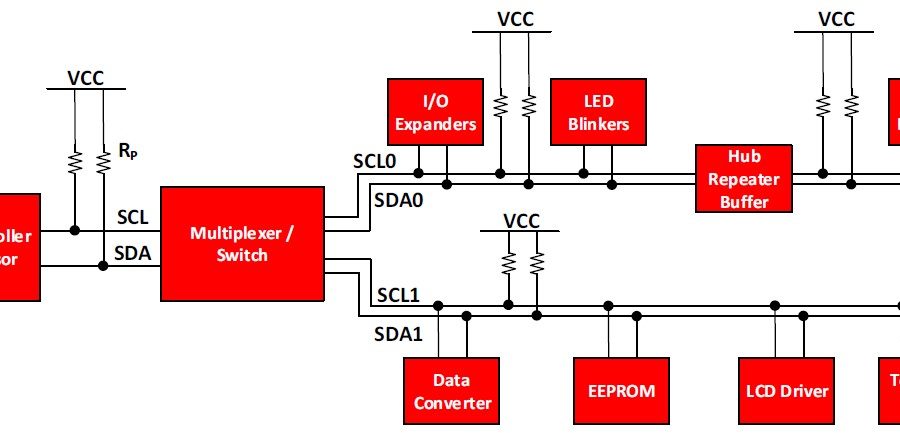

The I2C bus is a very popular and powerful bus used for communication between a master (or multiple masters) and a single or multiple slave device.

The Bus included only two lines – a serial data line (SDA) and a serial clock line (SCL). The Master is an essential component of the protocol’s integrity and has several important tasks. It’s drives the SCL, controls the SDA, can write data to a slave, and can read data from a salve. In this project we have conducted the full process of implement a component. We design an I2C Master controller capable to execute all the tasks mentioned above. Implemented the I2C Master as an IP block using Xillinx Vivado.

Test it’s functionality by simulations that included writing and reading data from luminosity sensor using Nexys-A7.