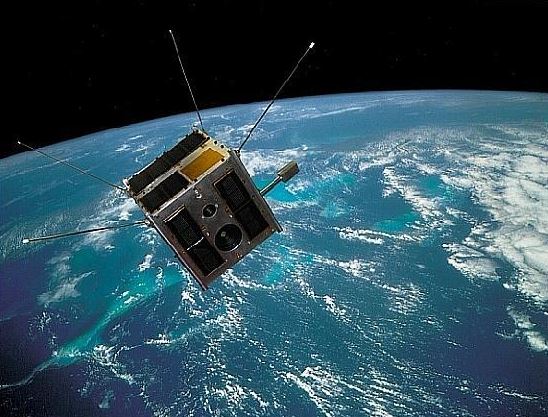

In a CubeSat communication satellite which is scheduled to be launched in Q2 2020, a FPGA is used to interface some analog RF components to the PCIe bus of a processor.

Up in space, the complete electronic of the satellite is subjected to a high degree of radiation.

Radiation may lead to temporary or even permanent malfunction of the components e.g. the FPGA. As less than half the FPGA is utilized,reprogramming the FPGA with a bit-stream avoiding the damaged areas may extend the mission time of the satellite.

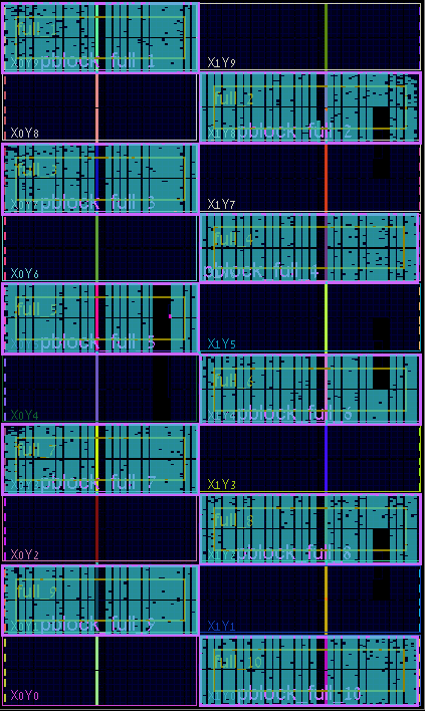

In order to know which areas have to be avoided when recompiling the design, the FPGA needs to be extensively tested. Developing methods for testing the FPGA is the aim of this project.

When in space, the high levels of radiation could cause damage to the

electronics components in a satellite, namely the FPGA.

The damage can be temporary (e.g. a single bit flips), or permanent (an

electrical component gets burnt).

This project is concentrated on developing a method to check the

functionality, and correctness, of the different components of the

FPGA:

• CLB (Configurable Logic Block).

• DSP (Digital Signal Processors).

• Memory.

The assumption we followed throughout this project was, that an error

that occurs more than once is considered to be permanent damage.

Furthermore, in this project we were looking to define the faulty area,

as it is extracted from the tests.

Later on, as a continuation to this project, it is possible to develop a

method to avoid the area marked as faulty, and find an alternative

usage of the FPGA, with the same functionality.

Through that, we believe the lifespan of the satellite can be

lengthened, and a loss of resources can be averted.

The project is divided into four main sections:

1 Understanding the different functional elements in the FPGA.

2 Developing a method of testing said elements.

3 Locating the faulty area (through loads).

4 Physical results via VIO (Virtual Input Output).

This project can be continued to find a post-error-discovery solution to

using the FPGA while avoiding the faulty areas, or adding checkpoints

along the way to further segregate the error; thus adding to the

system’s lifespan and extending the mission.