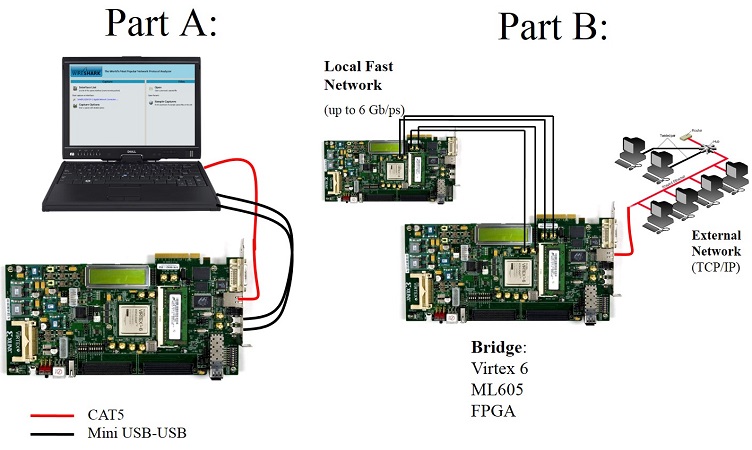

Implementing FPGA Bridge between High Speed Channel (Local Network) & Ethernet (External Network). The conception is to create a mutual environment (accelerator) to provide the ability to communicate between the two networks with high rates, utilizing the high capabilties of the Xilinx Virtex 6 FPGA.

This project consists of two parts:

1. Acquaintance in depth with the Xilinx working environment and tools, and implementing an internal loopback (first semester).

2. Creating the bridge itself by implementing the networks’ protocols, and enabling communication between them (second semester).