The goal of this project is to enhance a design of a basic CFMT architecture and test the performance by running SPEC CPU 2006 benchmarks.

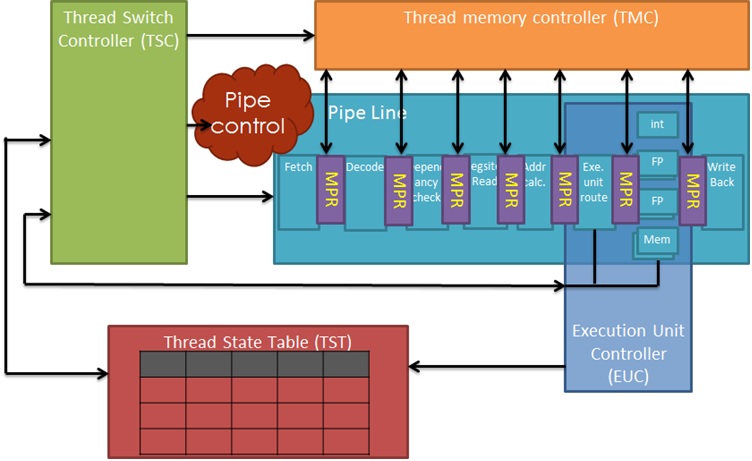

Emerging memory technologies enable new computer architectures, previously discarded due to dense memory requirements. In this project we implement on an FPGA such an architecture called Continuous Flow Multi-Threading (CFMT) – a Switch on Event Multi-Threading (SoE MT) extension that reduces switch penalty by storing the thread state in adjacent registers. We extended an earlier HDL design, which succeeded in simulating such an architecture, to hook up to FPGA environment and comply with design rules. Such an FPGA implementation stresses physical constraints, and is used to evaluate the architecture with industry standard benchmarks. In this report we describe the architecture in detail, go over the implementation process and environment and compare benchmark performance to standard SoE.