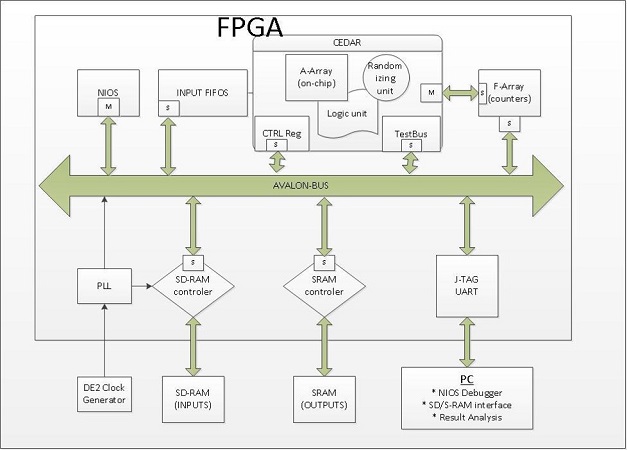

In our project, we will design the implementation for the CEDAR algorithm over Hardware Description Language, and using functional simulations, we will demonstrate how the CEDAR algorithm can achieve low relative errors while keeping a small number of bits per counter.

Network management applications require large numbers of counters in order to collect traffic characteristics for each network flow. However, these counters often barely fit into on-chip SRAM memories. Past papers have proposed using counter estimators instead, thus trading off counter precision for a lower number of bits. However, these estimators still use a significant amount of memory, and cannot always scale to arbitrary counter values.

The CEDAR algorithm proposes to decouple the counter estimators from their estimation values, which are quantized into estimation levels and shared among many estimators. These decoupled and shared estimation values enable us to easily adjust them without needing to go through all the counters.