Speed Digital System Laboraros

# A research & teaching laboratory

http://diglab.technion.ac.il

### **Activities**

### <u>Academic</u>

Course - High-Speed Digital Systems Design Lecturer – Dr. M. Werner

### Research

High speed PCB & IC technologies Peta Cloud – Fast optic network for data centers

### Lab. Educational Activities

**Projects** – 30 projects yearly (~60 students) **Experiments** (~400 students yearly)

- 1. High Speed Circuits (Signal Integrity)

- 2. SOPC Experiment

- 3. Jitter phenomenon

## **Laboratory Staff**

**Academic supervisor : Professor Tzahi Birk**

Staff:

**Laboratory manager: Mony Orbach**

**Application Engineer: Ina Rivkin**

**Projects coordinator:** Eli Shoshan

## **Projects development**

## **During corona pandemic days**

- Unfortunately corona is her to stay so we must adapt

- All presentations will be done on zoom

- All supervisor students meeting will be done on zoom

- When necessary, the lab will lend equipment to students for project development at home.

- All the lab staff are available on zoom for questions and problem solving

Last semester we all work with zoom, all and all it works!

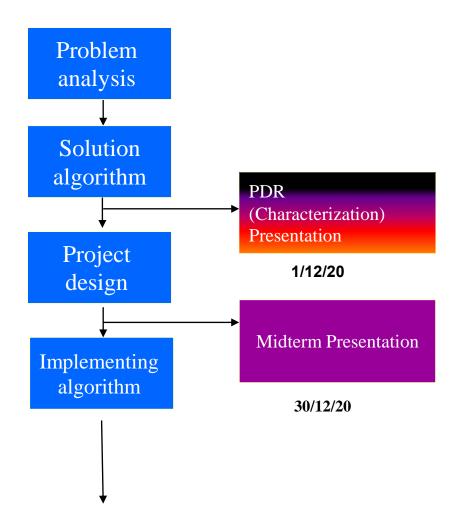

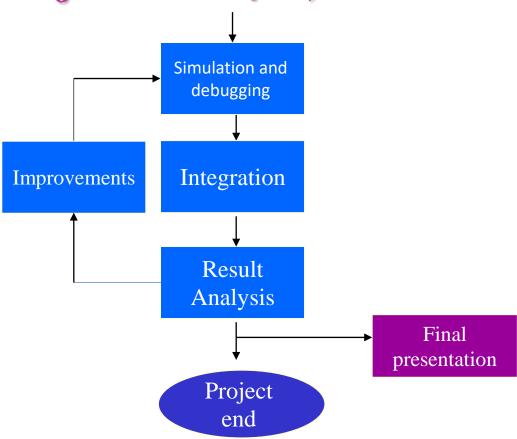

## **Project – Life cycle**

## Project – Life cycle, cont...

# PDR – Preliminary Design Review Presentation

1/12/20

- Motivation/Background

- Project goals

- Development environment

- Software development platforms

- Hardware development platforms

- Project Top Block diagram

- project inputs & outputs

- Function

- Project Gantt (time table) per week

- till MidTerm presentation

Registration to PDR presentation in Labadmin you coordinate with project supervisor

## **Project Management**

- 1. Project supervisor is your **first** help source.

- 2. Supervisor weekly meeting is mandatory!

- Set a day and time for weekly meeting

- 3. Schedule a weekly working hours on the project

- 4. The lab staff is your second help source.

Use Us!

### **Lab Rules**

#### 1. Lab safety procedure

- a. Follow the safety training

- b. Do not work alone

#### 2. Lab entrance rules

- a. Only students working on the project.

- b. Do not leave the door open.

#### 3. Lab Behavior rules

- a. No food or drinks

- b. Do not "fix" lab equipment

### עבודה מרחוק - Corona Time

- .1 מצגות פרויקטים ופגישות עם מנחים וצוות המעבדה יתקיימו בזום.

- ברות לרשת טכניונית מכל מקום <u>VPN</u> .2 <a href="https://cis.technion.ac.il/central-services/communication/off-campus-connection/otp/">https://cis.technion.ac.il/central-services/communication/off-campus-connection/otp/</a>

- diglabapps.ef.technion.ac.il שימוש בשרת אפליקציות 3

- . רישיונות והתקנת תוכנות בבית תאום מול אינה בצורה פרטנית ותלוי תוכנה.

- ביתה.  $\mathbf{z}$ יוד הביתה.  $\mathbf{5}$

- .6 במקרים שחייבים להגיע פיזית לטכניון נא לתאם אתנו מראש.

- ... **נא לפנות אלינו בכל בעיה שמתעוררת** ננסה לתת פתרון לכל בעיה.

- <u>כניסה למעבדה</u> יש לקודד את כרטיס הסטודנט ע"מ לפתוח את דלת המעבדה.

- .(TD-EF) מתבצעת ע"י שימוש בחשבון פקולטי (דומיין TD-EF).

- לצורך עבודה על הפרויקט לכל קבוצה הוקצתה מחיצה עם שטח דיסק נוסף.

- המיפוי לתיקייה מתבצע אוטומטית בכל מחשבי המעבדה.

- P: המחיצה תמופה לכונן

- ניתן להתחבר למחיצה בכל מחשב אחר מחוץ למעבדה ע"י מיפוי הכונן ל-

$\132.68.62.3\$  Projects  $\012020\$  Prj\_<מס' קבוצה>

- .(פרט למדריך C:\TEMP שתוכנו ימחק מדי פעם).

- P: את הקבצים יש לשמור בחשבונכם בדיסק השרת המוגדר ככונן

- <u>שרת אפליקציות</u>

remote desktop – התחברות ע"י שימוש ב – diglabapps.ef.technion.ac.il

### **Main Development tools**

#### FPGA flow

FPGA design

FPGA Simulation

FPGA Debugging

HLS – High Level Synthesis

C -> H

Embedded systems – Hardware & Software

ARM

Microblaze

- Xilinx

- Altera (Intel FPGA)

- Mentor

#### Enbedded Systems

- TI- Code Composer Studio

- Arduino

#### System Design

• LabView

#### **Board design & SI Simulation**

Schematic Capture PCB

SI Simulation

Cadence

#### Algorithm Development

HDL code Generation & Hardware in the Loop

• Matlab

DSP Builder System Generator HDL Coder

#### Software development

- Microsoft Visual Studio

- Embedded software tools

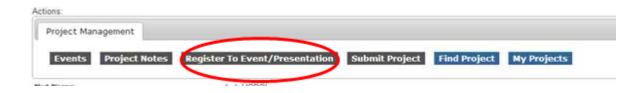

• הרישום למצגת מתבצע באתר labadmin.ef.technion.ac.il יבחירת המועד הרצוי. register to Event/Presentation ע"י כניסה לפרויקט, לחיצה על

הרישום למצגת אפיון (PDR) החל. נא להירשם בהקדם

## http://diglab.technion.ac.il/ אתר המעבדה

#### About High Speed Digital Systems Laboratory

The Prof. Israel Cederbaum High Speed Digital Systems Laboratory (HS-DSL) has been established in 1964 as a research and teaching laboratory, to train students in up to date digital techniques. The High Speed Digital Systems Lab focuses on quality education and research at the cutting edge of digital system technology. Our graduates move on to assume important positions in the High-Tech industry. Using its breadth and ability to build systems that really work, the Lab reaches out to apply its core expertise in diverse domains such as Medical Sensing, Signal Processing, Internet of Things, High Speed Digital Communication, and Intelligent Computing. HSDSL has strong connections and collaborations with both industry and academia, in Israel and worldwide. This provides a vital channel to exchange ideas and technology, promoting future research and development. The Lab puts strong emphasis on projects and research that benefit society.

# Thank you!