Method for accelerating simulation on FPGA using SW model on FPGA’s embedded CPU.

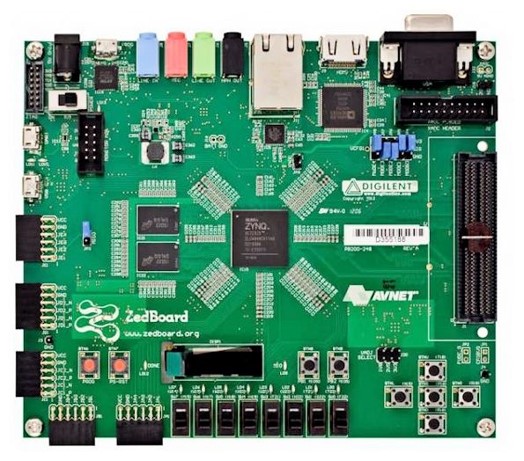

FPGA are programmable hardware components.

These days components are very big and are capable of containing a processor and a I/O and memory system – SOPC.

In order to deal with hardware validation in software , which may take a very long time, there is a need of an acceleration function that the processor may run and shorten this time of verification.