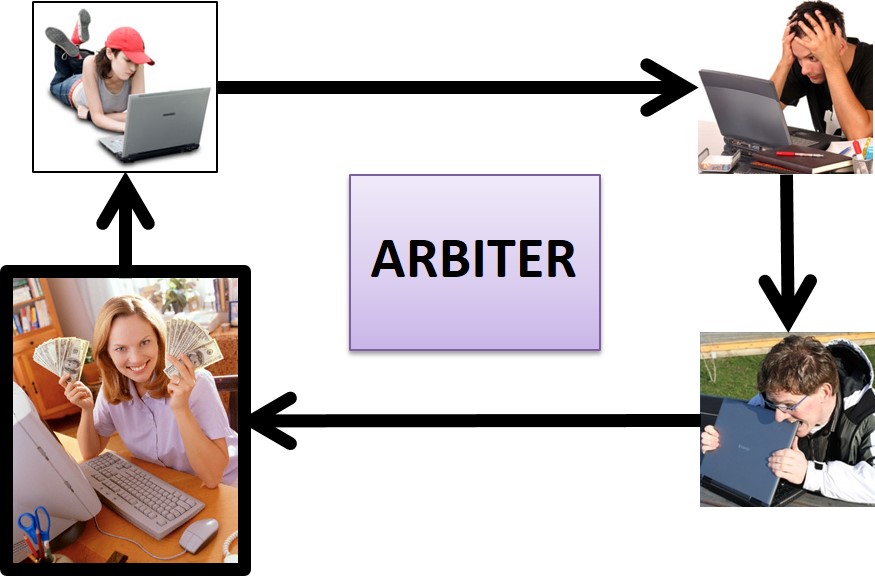

WRR algorithm (Weighted Round Robin) arbitrates between clients, requesting usage of the same resource. Arbitration is based on a simple round robin algorithm (clients are granted in a cyclic order), but the grant period for each client is related to its current weight. The project goal is to implement a WRR Arbiter on an FPGA with RT configurable weights. The WRR ARBITER design is implemented on a Cyclone II FPGA (on a DE2 board) and interacts with the switches and LEDs on the board as requests and grants. Interaction with a GUI on a PC as a host via RS232 enables full access to the system registers - RT configuration and performance reports.

Many of today’s systems contain at least one important resource that is to be shared between different users or sub-systems. Examples for such resources can be data buses, shared memories, I/O ports and more. While the simple round robin algorithm arbitrates the use of a resource in a ‘fair’ but simple and non optimal way, the weighted round robin algorithm enables optimization of the arbitration to match the application needs. The design detailed herein, implements an advanced WRR arbiter with the features of real time configuration, arbitration tracking for analysis and more.