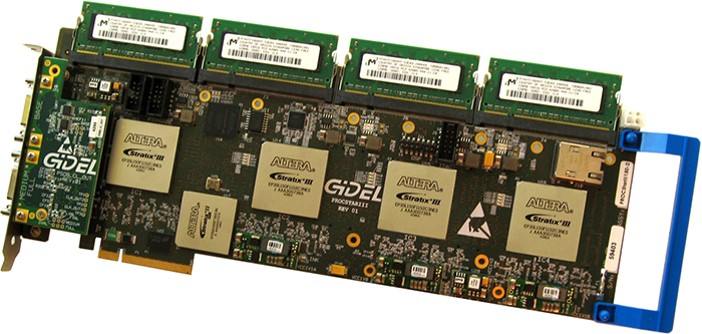

This project aims to Implement a video analysis designs on GIDEL PROCSTAR III platform that will enable usage and exploration of a new development platform (PART I – PROCHILs, PART II – PROCWIZARD, PROCAPI, PROCMegaFIFO ) and prepare a clear user-guide that will enable a fast and simple ramp-up of the tools and the appropriate flow.

Gidel Proc HIL is a Hardware-In-the-Loop acceleration tool for running Simulink designs on FPGAs. Using Proc HIL may significantly speed up the design development task.

Proc HIL enables the user to automatically translate Simulink designs into FPGA code and run this code under Simulink. This generated code is compatible with the PROC board.

Proc HIL generates a raw bit format (.rbf) file from the original Simulink design.

The main advantages using Proc HIL are:

- The Proc HIL generation tool block, when added to an existing design, automatically performs the whole generation process.

- When generation is finished, the original Simulink design is automatically replaced with a single HIL block which has all the inputs and outputs that were present in the original Simulink design. The HIL block configures the board and communicates with it to synchronize the simulation with the hardware running on the FPGAs.

- Dramatically improves simulation speed, with a dedicated accelerator for Simulink designs- allow you to simulate your design in the Simulink environment before loading it on the hardware.

- Allows you to design in a Simulink (block diagram based) environment, which is often simpler, faster and better understandable to the designer and the customer/ viewer.