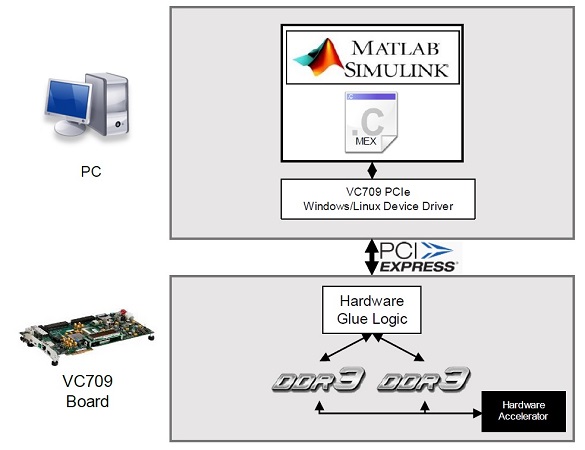

Building an infrastructure for hardware accelerators based on FPGAs for algorithms implemented in MATLAB.

Consists of 3 main parts:

- C code that is invoked from a MATLAB script (MEX file).

- PCIe driver that is used to transfer data to the hardware.

- Basic hardware design that connect the PCIe and the DDR3 memory DIMMs on the VC709 board.

This project implements the “pipe” between a host PC to a hardware accelerator implemented on the FPGA of the NetFPGA SUME development board.

It transfers data from the host PC through the PCIe interface, using a DMA engine, to a memory device on the board.

The project is based on a reference design from RIFFA -a framework for building systems with DMA data transfers. See http://riffa.ucsd.edu/ for more details.